|

|

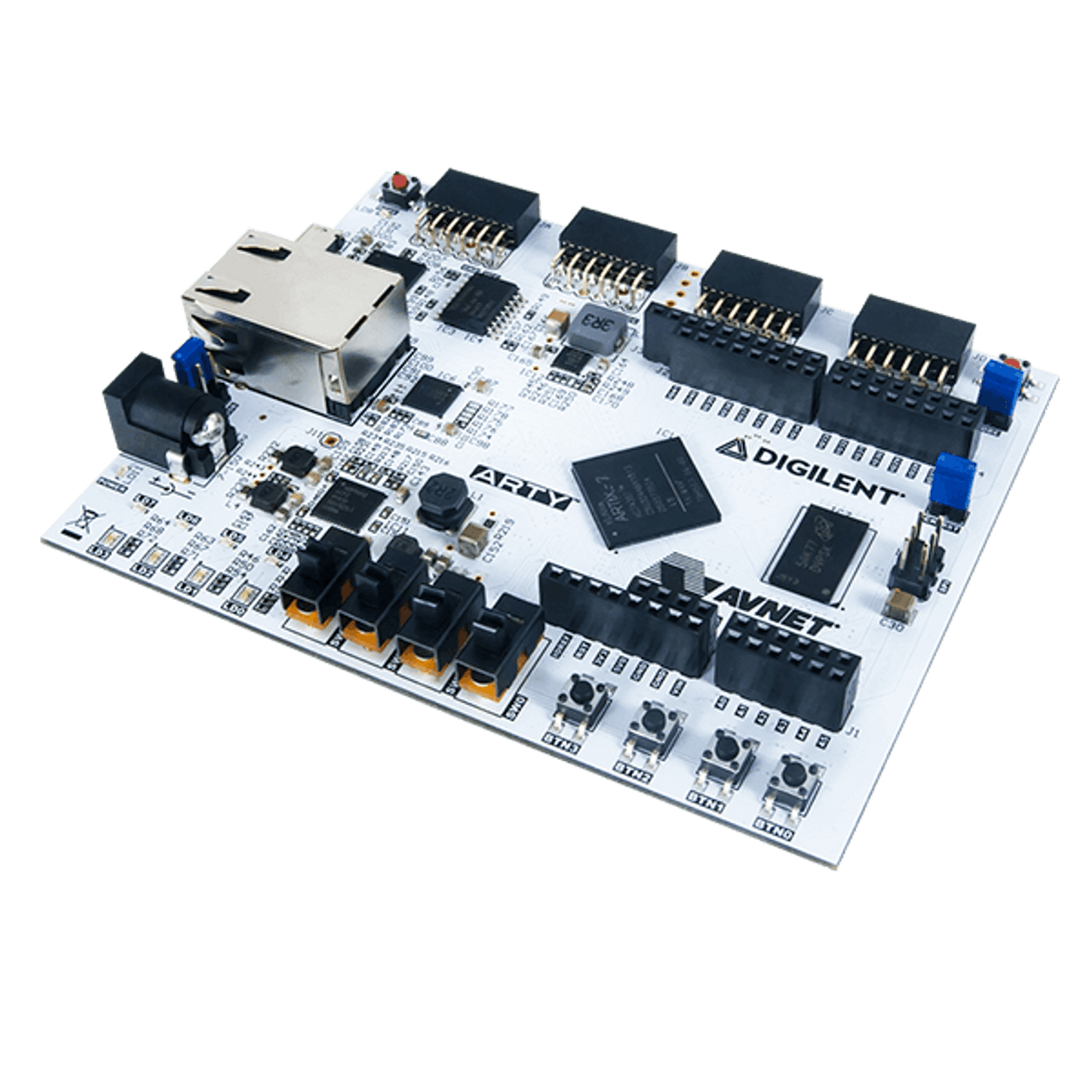

FeMiPulse I. FPGA-based pulse programmer. Programming interface: TCP-IP. Fully integrated into SpecMan4EPR.

4096 delays with 2.5ns-2s duration, 16 outputs, 1 level of cycles, 64k repetitions. Built-in hardware timing protection circuitry for magnetic resonance pulse outputs and programmable clock output. Variety of front-ends.

Overclocked 2ns and USB versions are on request.

|

FeMiPulse II. FPGA-based pulse programmer. Programming interface: TCP-IP. Fully integrated into SpecMan4EPR.

16384 delays with 4ns-316h duration, 16 outputs, 4 levels of nested cycles. External trigger. Zero service time cycles, exact sequence.

Built-in protection circuitry and programmable clock output.

Variety of front-ends.

|